## Diseño de un circuito integrado CMOS para codificador de prioridad de 8 a 3 líneas

Design of a CMOS Integrated Circuit for an 8-to-3 Line Priority Encoder

Rosaura Olvera Martínez <sup>1</sup>

Juan Pablo Ocampo Flores <sup>2</sup>

José Luis González Vidal <sup>3</sup>

Heberto Gómez Pozos <sup>4</sup>

Juan José Raygoza Panduro <sup>5</sup>

Universidad Autónoma del Estado de Hidalgo, Hidalgo, MÉXICO

<sup>1</sup> ORCID: 0009-0000-2683-9144 / ol447981@uaeh.edu.mx

<sup>2</sup> ORCID: 0009-0006-6988-5291 / oc384357@uaeh.edu.mx

<sup>3</sup> ORCID: 0000-0001-9482-0875 / jlvidal@uaeh.edu.mx

<sup>4</sup> ORCID: 0000-0001-8867-8534 / gpozos@uaeh.edu.mx

Universidad de Guadalajara, Jalisco, MÉXICO

<sup>5</sup> ORCID: 0000-0002-8567-4981 / jlvidal@uaeh.edu.mx

juan.rpanduro@academicos.udg.mx

Recibido 08/07/2025, aceptado 10/11/2025.

## Resumen

El presente trabajo consiste en el diseño de un codificador de prioridad (priority encoder) en un circuito integrado (CI) con tecnología CMOS, basado en el chip 74LS148 de Texas Instruments (TI). Éste es un circuito digital muy utilizado especialmente en el diseño de sistemas digitales y microprocesadores. Su función principal es convertir múltiples entradas activas en una salida binaria representativa, dando prioridad jerárquica a las entradas. También se considera como un bloque fundamental, debido a su capacidad de gestionar múltiples eventos simultáneamente y decidir cuál de ellos se debe atender primero. El chip propuesto fue diseñado con la herramienta L-Edit de Mentor Graphics, junto con todos los cálculos necesarios para poder establecer el ancho (W) y la longitud (L) del canal de los transistores diseñados, todo esto para poder implementar un CI de un decodificador con un consumo menor de potencia y un rango más amplio de operación. Con el desarrollo de este chip se busca fomentar la independencia tecnológica del país. La tecnología CMOS por sus siglas en inglés Complementary Metal Oxide Semiconductor, está basada en transistores de efecto de campo que, con el paso de los años ha ganado popularidad en los circuitos integrados (CI), su característica principal es el bajo consumo de potencia, la velocidad de commutación y alta inmunidad al ruido.

**Palabras clave:** circuitos integrados, CMOS, codificador.

2

## Abstract

The aim of this work is the design of a priority encoder in an integrated circuit (IC) with CMOS technology, based on the Texas Instruments (TI) 74LS148 chip. This digital circuit is widely used, especially in the design of digital systems and microprocessors. Its main function is to convert multiple active inputs into a representative binary output, hierarchically prioritizing the inputs. It is considered a fundamental building block, due to its ability to handle multiple events simultaneously and decide which one should be attended to first. The proposed chip was designed using the L-Edit tool from Mentor Graphics, along with all the necessary calculations to determine both channel width (W) and length (L) of the designed transistors, to implement a decoder IC with lower power consumption and a wider operating range. Furthermore CMOS (complementary metal-oxide-semiconductor) technology is based on field-effect transistors, which, over time, have gained popularity in integrated circuits (ICs). Its main features are low power consumption, switching speed and high noise immunity.

**Index terms:** integrated circuits, CMOS, encoder.

## I. INTRODUCCIÓN

En la industria de los semiconductores a nivel mundial la tecnología TTL es la más utilizada, como un consumo de potencia media además de ser una opción de bajo costo. A pesar de eso la tecnología Metal Óxido Semiconductor complementario (CMOS) ha ganado relevancia con el paso del tiempo, por sus amplias ventajas entre las que se encuentran menor consumo de energía, mayor tolerancia al ruido, diseño mucho más sencillo y conmutación con mayor rapidez.

Los transistores MOS (Metal Óxido Semiconductor) son dispositivos semiconductores formados por un sustrato de silicio dopado, sobre el cual se hace crecer una capa de óxido de silicio ( $\text{SiO}_2$ ). Los elementos se conectan con dos terminales metálicas llamadas sustrato (Bulk) y la compuerta (Gate). La estructura se compara con un condensador de placas paralelas, en donde se remplaza una de las placas por el silicio semiconductor del sustrato, y la otra por un metal. Mas no tiene una estructura de unión pn; en cambio, la compuerta del MOSFET está aislada del canal mediante una capa de  $\text{SiO}_2$  [1], [2].

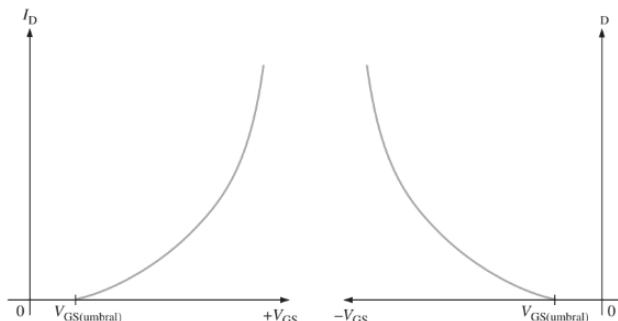

Hay dos tipos de transistores MOS: PMOS (MOS tipo p o canal p) y NMOS (MOS tipo n o canal n). Por consiguiente, un MOS canal n requiere un voltaje positivo de compuerta a fuente  $V_{gs}$  y un MOS canal p requiere un voltaje negativo de compuerta a fuente  $-V_{gs}$ . La Fig. 1 muestra las curvas características de transferencias general para ambos tipos de MOSFET.

Figura 1. Curvas de la característica de transferencia general de un MOSFET.

La principal característica de los CMOS consiste en el conjunto de transistores de tipo PMOS y NMOS configurados de tal manera que, en estado de reposo, el consumo de energía es debido a las corrientes parásitas. [3], [4], [5].

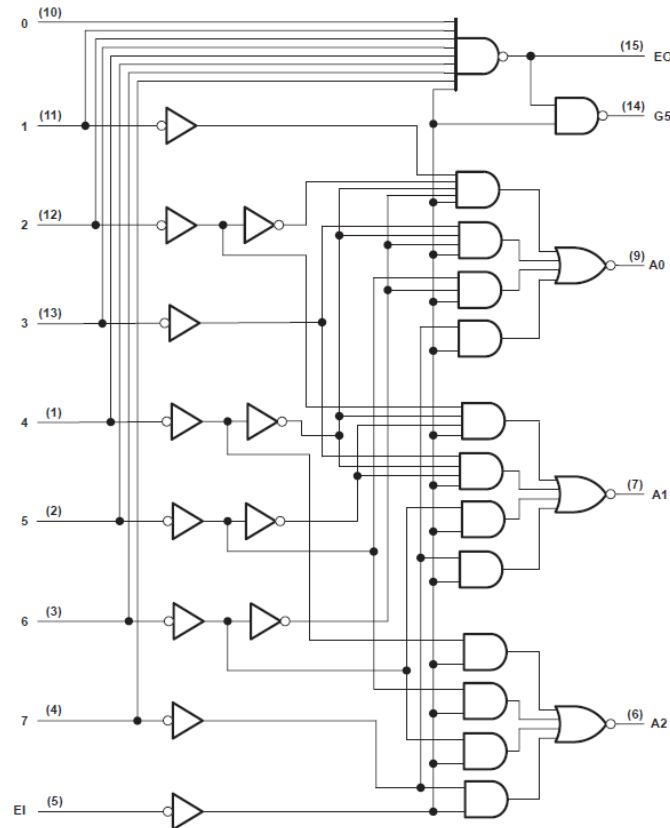

El 74LS148 de Motorola® es un Codificador prioritario de 8 a 3 líneas que se utiliza como registro de 8 bits. Cuenta con 8 entradas de datos, una entrada de reloj, una entrada de habilitación y ocho salidas que representan los datos almacenados en el registro, el diagrama esquemático del 74LS148 se muestra en la Fig. 2, y la tabla 1 muestra su tabla de verdad [6], [7], [8].

Los codificadores de prioridad se utilizan principalmente en el control de sistemas digitales para gestionar entradas que pueden ocurrir simultáneamente, seleccionando y procesando la de mayor prioridad. Sus aplicaciones más importantes pueden ser controladores de interrupciones en microprocesadores, codificación de teclado, sistemas de comunicación, conversión analógica a digital, sistemas domóticos y de monitoreo, gestión de recursos.

Figura 2. Diagrama Lógico del 74LS148.

TABLA 1

TABLA DE VERDAD DEL 74LS148.

| EI | Entradas |   |   |   |   |   |   | Salidas |    |    |    |    |    |

|----|----------|---|---|---|---|---|---|---------|----|----|----|----|----|

|    | 0        | 1 | 2 | 3 | 4 | 5 | 6 | 7       | A2 | A1 | A0 | GS | EO |

| H  | X        | X | X | X | X | X | X | X       | H  | H  | H  | H  | H  |

| L  | H        | H | H | H | H | H | H | H       | H  | H  | H  | H  | L  |

| L  | X        | X | X | X | X | X | X | L       | L  | L  | L  | L  | H  |

| L  | X        | X | X | X | X | X | L | H       | L  | L  | H  | L  | H  |

| L  | X        | X | X | X | X | L | H | H       | L  | H  | L  | L  | H  |

| L  | X        | X | X | X | L | H | H | H       | L  | H  | H  | L  | H  |

| L  | X        | X | X | L | H | H | H | H       | H  | L  | L  | L  | H  |

| L  | X        | X | L | H | H | H | H | H       | H  | H  | L  | L  | H  |

| L  | X        | L | H | H | H | H | H | H       | H  | H  | L  | L  | H  |

| L  | L        | H | H | H | H | H | H | H       | H  | H  | H  | L  | H  |

H = Nivel lógico alto, L = Nivel lógico bajo, X = No importa

El propósito del este trabajo es la implementación de compuertas lógicas AND, NAND, NOR, NOT y BUFFER NEGADO con tecnología CMOS para su utilización en el circuito integrado 74LS148 mejorando el consumo de este.

## II. DESARROLLO

### A. Ecuaciones

Las siguientes ecuaciones se emplearon para poder determinar la L y W para poder calcular las corrientes de drenador-fuente ( $I_{DS}$ ) de los transistores NMOS y PMOS para las compuertas lógicas utilizadas; primeramente, se debe de conocer el voltaje de umbral de ambos transistores siendo (1) para NMOS y (2) para PMOS. Las variables calculadas son  $V_{TH}$ ,  $V_{THP}$ ,  $\phi_b$ ;  $C_{ox}$ ; las variables propuestas son  $V_{FB}$ ,  $N_A$ ,  $N_D$ ,  $T$ ,  $t_{ox}$  y, las constantes utilizadas  $k$ ,  $q$ ,  $n_i$ ,  $\epsilon_{Si}$ ,  $\epsilon_{SiO_2}$ .

$$V_{THN} = V_{FB} + 2\phi_{bn} + \frac{\sqrt{2\epsilon_{Si}qN_A2\phi_{bn}}}{C_{ox}} \quad (1)$$

$$V_{THP} = V_{FB} - |2\phi_{bp}| - \frac{\sqrt{2\epsilon_{Si}qN_D|2\phi_{bp}|}}{C_{ox}} \quad (2)$$

$$\phi_b = \frac{kT}{q} \ln \frac{N_A}{n_i} \quad (3)$$

$$C_{ox} = \frac{\epsilon_{SiO_2}}{t_{ox}} \quad (4)$$

Donde:

$V_{TH}$ : Voltaje de umbral

$\phi_b$ : Potencial del substrato

$V_{FB}$ : Voltaje de banda plana (-0.9V para (1) y -0.2V para (2))

$\epsilon_{Si}$ : Permitividad del silicio ( $1.06 \times 10^{-12} \text{ F/cm}$ )

$q$ : Carga del electrón ( $1.6 \times 10^{-19} \text{ C}$ )

$N_A$ : Densidad de las impurezas aceptoras

$N_D$ : Densidad de las impurezas donadoras

$C_{ox}$ : Capacitancia del óxido de compuerta

$k$ : Constante de Boltzmann ( $1.381 \times 10^{-23} \text{ J/K}$ )

$T$ : Temperatura en grados Kelvin

$n_i$ : Concentración intrínseca del silicio ( $1.5 \times 10^{-12} \text{ F/cm}$ )

$\epsilon_{SiO_2}$ : Permitividad del óxido de silicio ( $3.4554 \times 10^{-13} \text{ F/cm}$ )

$t_{ox}$ : Espesor del aislante de la compuerta

Una vez definidas las fórmulas se procedió a sustituir los valores. Para esto  $N_A$  y  $N_D$  se fijan en  $1.1 \times 10^{16} \text{ cm}^{-3}$  y el  $t_{ox}$  de 65nm que es igual a  $6.5 \times 10^{-6} \text{ cm}$ .

Posteriormente se define el potencial del substrato (3) a una temperatura de 300ºK equivalente a 26. 85ºC

$$\phi_{bn} = \phi_{bp} = \frac{(1.381 * 10^{-23} \text{ J/K})(301.3 \text{ K})}{1.6 * 10^{-19} \text{ C}} * \ln\left(\frac{1.1 \times 10^{16} \text{ cm}^{-3}}{1.5 \times 10^{10} \text{ cm}^{-3}}\right) = 349.7 \text{ mV}$$

Además de esto se tiene que calcular la capacitancia del óxido de la compuerta con la ecuación (4)

$$C_{ox} = \frac{3.4554 \times 10^{-13} \text{ F/cm}^3}{6.5 \mu\text{cm}} = 53.16 \text{ nF/cm}^2$$

Con los resultados anteriores se pueden calcular los voltajes de umbrales de los NMOS (1)

$$V_{THN} = -0.9 \text{ V} + 2(349.7 \text{ mV}) + \sqrt{\frac{2(1.06 \times 10^{-12} \frac{\text{F}}{\text{cm}})(1.6 \times 10^{-19} \text{ C})(1.1 \times 10^{16} \text{ cm}^{-3})(2 * 349.7 \text{ mV})}{53.16 n \frac{\text{F}}{\text{cm}^2}}}$$

$$V_{THN} = 760.35 \text{ mV}$$

Prosiguiendo con el PMOS

$$V_{THP} = -0.2 \text{ V} - 2|349.7 \text{ mV}| - \sqrt{\frac{2(1.06 \times 10^{-12} \frac{\text{F}}{\text{cm}})(1.6 \times 10^{-19} \text{ C})(1.1 \times 10^{16} \text{ cm}^{-3})|2(349.7 \text{ mV})|}{53.16 \text{ nF/cm}^2}}$$

## 6

$$V_{THP} = -1.46 \text{ V}$$

A continuación, se calculan  $\beta_n$ ,  $\beta_p$ ,  $I_{ds}$  e  $I_{sd}$  de los transistores con las siguientes ecuaciones:

$$\beta_n = \frac{\mu_n * \epsilon_{SiO_2} W}{t_{ox}} \quad (5)$$

$$\beta_p = \frac{\mu_p * \epsilon_{SiO_2} W}{t_{ox}} \quad (6)$$

$$I_{ds} = \frac{\beta_n(V_{gs} - V_{THN})^2}{2} \quad (7)$$

$$I_{sd} = \frac{\beta_p(V_{sg} - |V_{THP}|)^2}{2} \quad (8)$$

Donde:

$\beta_n$ : Constante Beta para los transistores NMOS

$\beta_p$ : Constante Beta para los transistores PMOS

$\mu_n$ : Movilidad Superficial de los electrones ( $500 \text{ cm}^2/\text{V}\cdot\text{sec}$ )

$\mu_p$ : Movilidad Superficial de los huecos ( $180 \text{ cm}^2/\text{V}\cdot\text{sec}$ )

$\epsilon_{SiO_2}$ : Permitividad del óxido de silicio ( $3.454 * 10^{-13} \text{ F/cm}$ )

$t_{ox}$ : Espesor del aislante de la compuerta

$W$ : Ancho de la compuerta

$L$ : Largo de la compuerta

$I_{ds}$ : Corriente entre el drenador y la fuente.

$I_{sd}$ : Corriente entre la fuente y el drenador.

$V_{gs}$ : Voltaje de compuerta a fuente

$V_{TH}$ : Voltaje de umbral

$V_{gs}$ : Voltaje compuerta fuente

Para el cálculo de  $\beta n$  con (5)

$$\beta n = \frac{\left(\frac{500\text{cm}^2}{V\text{sec}}\right) \left(3.4554 * 10^{-13} \frac{\text{F}}{\text{cm}}\right) W}{6.5\mu\text{cm}} \frac{A}{L}$$

$$\beta n = 26.58\mu \frac{A}{V^2} \frac{W}{L}$$

Prosiguiendo con el cálculo de  $\beta p$  con (6) se obtiene:

$$\beta p = \frac{\left(\frac{180\text{cm}^2}{V\text{sec}}\right) \left(3.4554 * 10^{-13} \frac{\text{F}}{\text{cm}}\right) W}{6.5\mu\text{cm}} \frac{A}{L}$$

$$\beta p = 9.5688\mu \frac{A}{V^2} \frac{W}{L} \approx 9.57\mu \frac{A}{V^2} \frac{W}{L}$$

## 7

A continuación, se calcula la  $W$  proponiendo para  $L = 0.5\mu\text{m}$ , un voltaje de  $V_{gs}$  de 5 V y la corriente  $I_{ds}$  de  $85\mu\text{A}$  con (7) para el transistor NMOS

$$I_{ds} = \beta n \frac{(V_{gs} - V_{THN})^2}{2} = 26.58\mu\text{m} \frac{A}{V^2} \frac{W}{L} \frac{(V_{gs} - V_{THN})^2}{2}$$

$$I_{ds} = 26.58\mu \frac{A}{V^2} \frac{W}{L} \frac{(5V - 760.35mV)^2}{2} = 238.88\mu\text{A} \frac{W}{L} \approx 239\mu\text{A} \frac{W}{L}$$

$$85\mu\text{A} = 239\mu\text{A} \frac{W_n}{0.5\mu\text{m}} \therefore W = \frac{85\mu\text{A}(0.5\mu\text{m})}{239\mu\text{A}}$$

$$W_n = 177.8\text{nm} \approx 0.18\mu\text{m}$$

Para el PMOS se propuso una corriente  $I_{sd}$  de  $100\mu\text{A}$  con  $L$  nuevamente de  $0.5\mu\text{m}$ , junto con el voltaje de  $V_{sg}$  de 5V (8)

$$I_{sd} = 9.57\mu \frac{A}{V^2} \frac{(5V - |-1.46V|)^2}{2} * \frac{W}{L}$$

$$I_{sd} = 59.96\mu\text{A} * \frac{W_p}{L} \therefore W_p = \frac{100\mu\text{A} * 0.5\mu\text{m}}{59.96\mu\text{A}} = 833.889\text{nm}$$

$$W_p \approx 0.83\mu\text{m}$$

## B. Comparación de Niveles Lógicos de 5V y 3.3V

A partir de las ecuaciones (7) y (8) se sustituyen los voltajes de  $V_{gs}$  y  $V_{sg}$  a 3.3V para demostrar los consumos más bajos

Para NMOS

$$I_{ds} = 26.58\mu \frac{A}{V^2} \frac{0.18\mu m}{0.5\mu m} \frac{(3.3V - 760.35mV)^2}{2} = 30.8585\mu A \approx 30.86\mu A$$

y PMOS

$$I_{sd} = 9.57\mu \frac{A}{V^2} \frac{(3.3V - |-1.46V|)^2}{2} * \frac{0.83\mu m}{0.5\mu m} = 26.8921\mu A \approx 27\mu A$$

En la tabla 2 se puede ver la comparación entre los diferentes niveles lógicos:

TABLA 2

CONSUMOS CON NIVELES LÓGICOS DE 5V Y 3.3V.

|      | Transistor | Voltaje (V) | Corriente ( $\mu A$ ) |

|------|------------|-------------|-----------------------|

| NMOS |            | 5           | 85                    |

|      |            | 3.3         | 30.86                 |

| PMOS |            | 5           | 100                   |

|      |            | 3.3         | 27                    |

Como se puede observar en la tabla anterior el consumo con un voltaje menor es proporcional a la corriente.

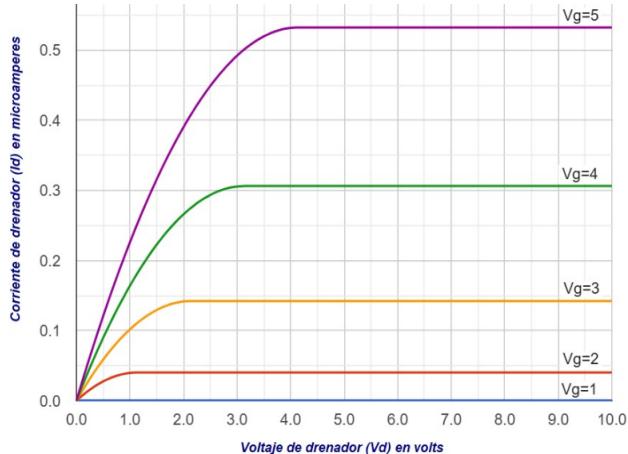

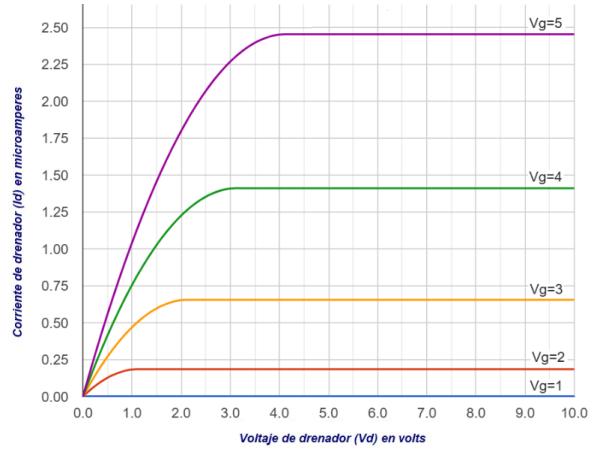

## C. Prueba del circuito en Multisim®

En esta sección se pueden observar las simulaciones en el software NI Multisim® comprobando que la saturación es correcta con los cálculos. Como se puede comprobar en las Fig. 3 y Fig. 4 los resultados en la simulación son muy prometedores, teniendo una diferencia muy pequeña a los cálculos realizados.

**Figura. 3.** Curvas de la característica de transferencia del NMOS modificado.

**Figura. 4.** Curvas de la característica de transferencia del PMOS modificado.

9

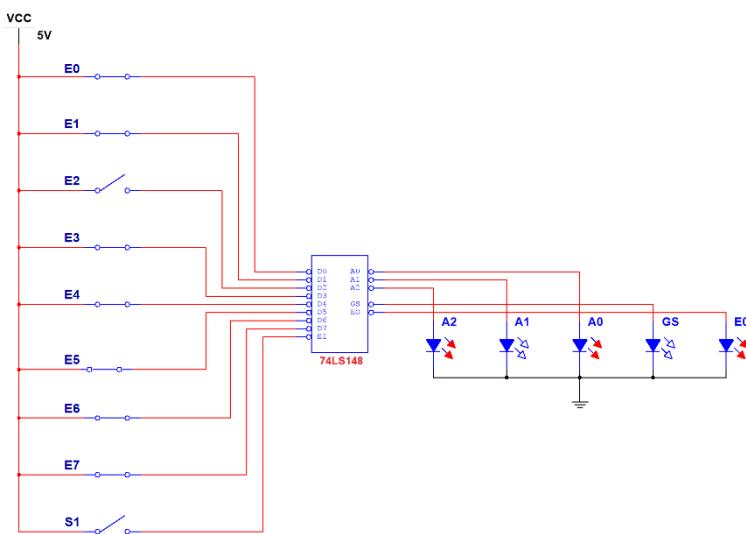

La Fig. 5 muestra la simulación del CI 74LS148, para este caso los switches S1 y E2 se encuentran abiertos, lo que conduce a que las salidas sean  $A_0=1$ ,  $A_1=0$  y  $A_2=1$ , correspondiente al 2 lógico en lógica invertida, para las salidas GS=0 y SE= 1.

**Figura. 5.** Diagrama esquemático de circuito de prueba del 74LS148.

### III. RESULTADOS

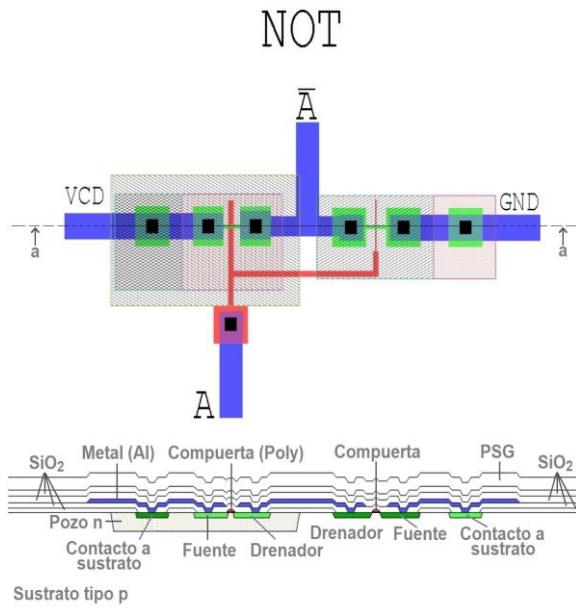

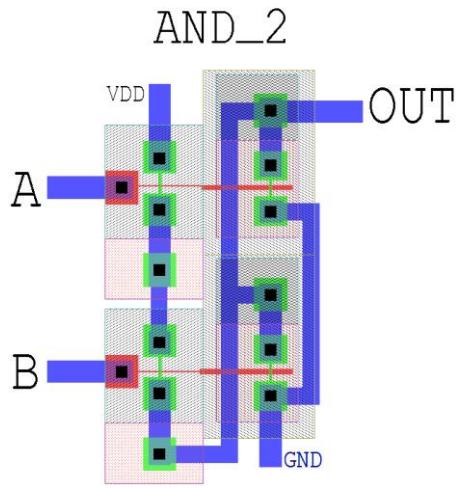

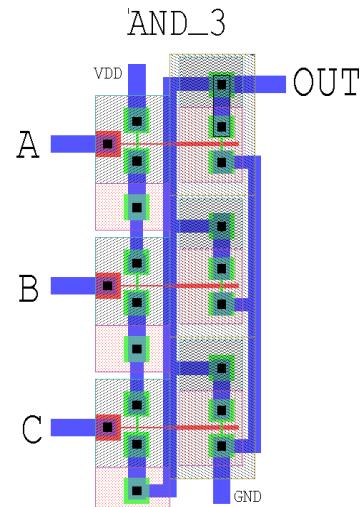

En esta sección se muestran los diseños de los layouts de las compuertas utilizadas internamente por el CI del 74LS148, éstas fueron diseñadas con software de diseño electrónico Tanner EDA de Mentor Graphics.

La fig. 6 se muestra el inversor y un corte transversal a-a, con las diferentes capas de materiales. Para el diseño del circuito integrado se consideró una oblea de silicio tipo p, y los pasos para la fabricación son: primero se implanta un pozo tipo n donde se construirá el transistor PMOS, para crear las zonas de fuente y drenador tipo p, posteriormente se deposita un óxido de silicio ( $\text{SiO}_2$ ) y se graba, el siguiente paso es depositar las regiones tipo n del transistor NMOS, a continuación se deposita otra capa de  $\text{SiO}_2$  y se graba, se deposita la capa de polisilicio o Poly (Poly-Si), que conforma la compuerta de los transistores, encima se depositan otra capa de  $\text{SiO}_2$  y el metal (Metal1), usualmente se utiliza aluminio (Al) para las conexiones eléctricas entre todos los transistores; dependiendo de la densidad del circuito integrado se pueden utilizar varios metales, es decir, varias capas de aluminio, para establecer puentes entre los transistores, finalmente encima de todo el circuito integrado se deposita una última capa de fosfósilicato (PSG) el cual protege el circuito integrado.

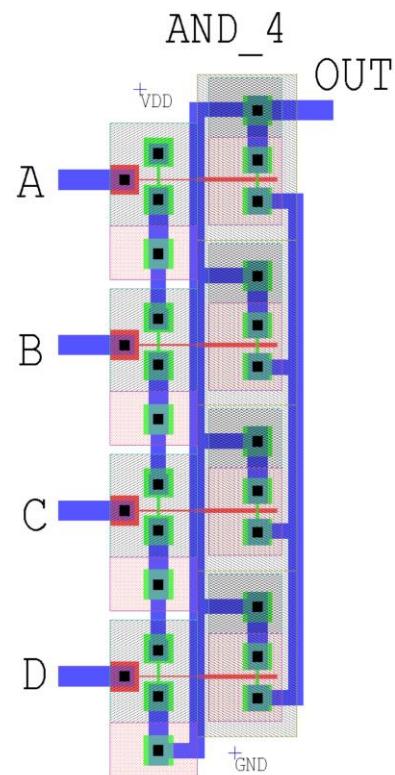

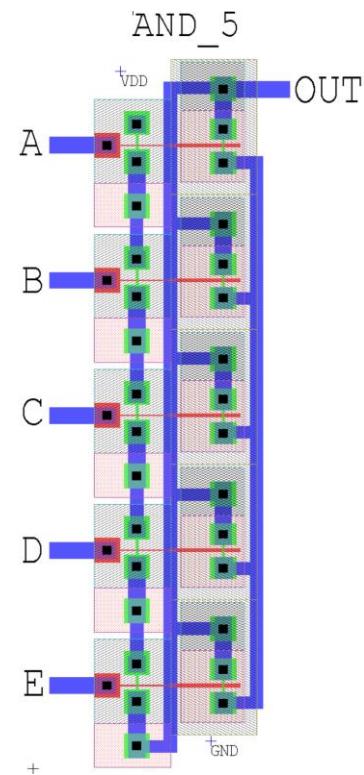

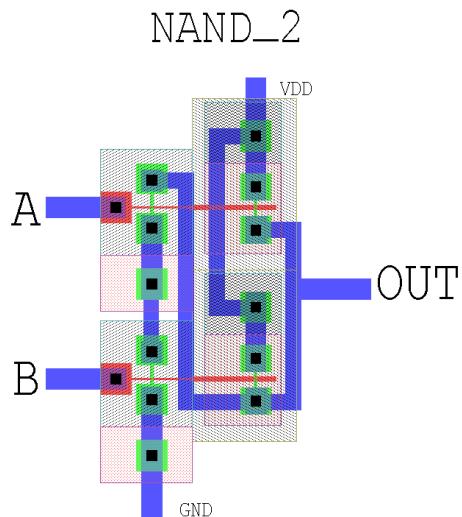

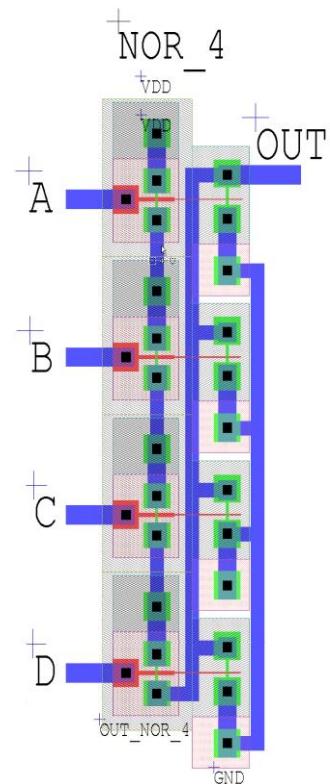

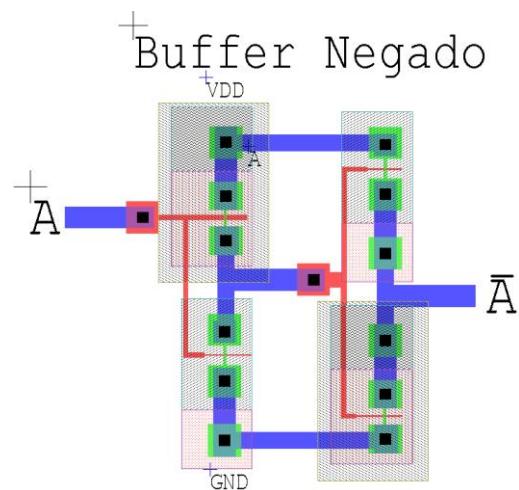

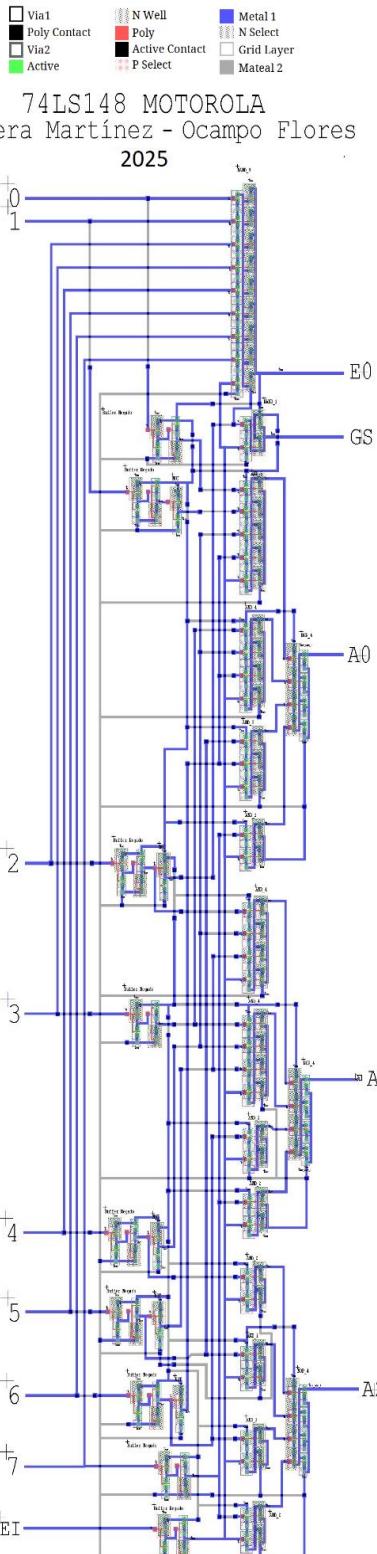

También se diseñaron compuertas AND de dos, tres, cuatro y cinco entradas mostradas en la Fig. 7; la compuerta NAND de dos entradas mostrada en la Fig. 8, compuerta NOR de cuatro entradas mostrada en la Fig. 9, un buffer negado mostrado en la Fig. 10 y, finalmente la Fig. 11 muestra el diseño completo de del layout del circuito integrado 74LS148 con transistores de la tecnología CMOS. En la parte derecha se aprecian las entradas de datos del 0 al 7 y la entrada de habilitación EI, por otra parte, a la izquierda se aprecian las salidas E0, GS, A0, A1 y A2. El área del circuito 517.6  $\mu\text{m}$  por 1981.1  $\mu\text{m}$ .

10

Figura. 6. Compuerta NOT (inversor).

a) Compuerta and con dos entradas.

b) Compuerta and con tres entradas

c) Compuerta and con cuatro entradas

d) Compuerta and con cinco entradas

Figura. 7. Compuertas AND con entradas múltiples.

12

Figura. 8. Compuertas NAND con dos entradas.

Figura. 9. Compuertas NOR con cuatro entradas.

Figura. 10. Buffer negado.

13

Figura 11. Layout del circuito integrado del 74LS148 completo.

## IV. CONCLUSIONES

En el presente trabajo se demostraron las ventajas de la tecnología CMOS utilizando el Circuito Integrado 74LS148 de Motorola® hecho a base de tecnología TTL, se diseñaron las compuertas lógicas AND de dos, tres, cuatro y cinco entradas, NAND de dos y nueve entradas, NOR de cuatro entradas, además el Inversor (NOT) y el Buffer negado. Con base a un consumo deseado se realizaron los cálculos para poder llegar a las dimensiones necesarias, dando como resultado los valores de longitud  $L$  y ancho del canal  $W$  y los respectivos voltajes de umbral de los transistores NMOS y PMOS, con una  $L_{n,p}$  de  $0.5 \mu\text{m}$   $W_n=0.18 \mu\text{m}$  y  $W_p=0.83 \mu\text{m}$  con voltajes de umbral  $V_{thn}=730.35\text{mV}$  y  $V_{thp}=-1.46\text{V}$ . Con estas dimensiones se diseñaron las compuertas de manera individual, posteriormente se interconectaron para formar el circuito integrado completo, cuyo layout fue diseñado con la herramienta L-Edit de Mentor Graphics. Además de requerir un mínimo consumo de potencia, el área utilizada es también mucho menor. Dando por área final del circuito  $517.6$  micras por  $1981.1$  micras, cabe destacar que es un prototipo. Las simulaciones de las compuertas se realizaron en NI Multisim™ V14.2 de National Instruments. Este tipo de proyectos resultarán útiles para la educación, investigación otras opciones para realizar circuitos integrados o incluso en sistemas embebidos donde su finalidad es optimizar recursos sin comprometer la funcionalidad. Como trabajo futuro se propone la implementación física del diseño.

### CRediT (Contributor Roles Taxonomy)

**Contribuciones de los autores:** Conceptualización: **JPOF**; Metodología: **ROM**; Software: **JPOF y ROM**; Investigación: **ROM**; Redacción y preparación del borrador original: **JLGV**; Redacción, revisión y edición: **HGP**; Supervisión: **JJRP**; Análisis formal: **JJRP y HGP**; Administración del proyecto: **JLGV**; Adquisición de fondos: No aplica.

**Financiamiento:** Los autores declaran que el proyecto fue desarrollado con recursos propios.

**Declaración de disponibilidad de datos:** Los datos se encuentran en el artículo.

**Agradecimientos:** Los autores agradecen al Laboratorio de Microelectrónica del CEDAI - UAEH.

**Conflictos de interés:** Los autores declaran que no existe conflicto de interés.

14

## REFERENCIAS

- [1] Fairchild Semiconductor, *CMOS, the Ideal Logic Family, Application Note 77*, San José, CA, USA: Fairchild Semiconductors, 1983, Available: <https://exa.unne.edu.ar/ingenieria/electronica3/pdf/AN-77%20CMOS,%20the%20Ideal%20Logic%20Family.pdf>

- [2] T. L. Floyd, *Dispositivos Electrónicos*, 8<sup>a</sup> ed., México: Pearson Education, 2010.

- [3] S. Acha Alegre *et al.*, *Electrónica digital: Introducción a la Lógica Digital: Teoría, Problemas y Simulación*, México: Alfaomega, 2003.

- [4] S. Noriega, *Familia lógica CMOS*, Argentina: Ministerio de Educación, Ciencia y Tecnología de la Nación, Instituto Nacional de Educación Tecnológica (INET), 2006. [Online] Available: <https://es.scribd.com/doc/100057275/Familia-logica-CMOS-Sergio-Noriega>

- [5] J. R. Yang, S. Han, *CMOS Integrated Circuit Design and Application*, USA: Sensors (MDPI), 2022, doi: <https://doi.org/10.3390/books978-3-0365-3478-7>

- [6] Motorola, *10-LINE-TO-4-LINE AND 8-LINE-TO-3-LINE PRIORITY ENCODERS - SN54/74LS147-SN54/74LS148, Hoja de especificaciones*, Available: <https://www.alldatasheet.es/html-pdf/5666/MOTOROLA/74LS148/258/1/74LS148.html>

- [7] M. Pérez Rodríguez, *Electrónica digital*, 2a. ed., México: ICB, 2015.

- [8] Y. Zhao, C. Lee, *Advanced CMOS Devices and Applications*, USA: Electronics (MDPI), 2024, doi: <https://doi.org/10.3390/books978-3-03928-594-5>